# EE 505

## Lecture 22

# ADC Design

- Folded

- Multi-Step Flash

- Pipeline

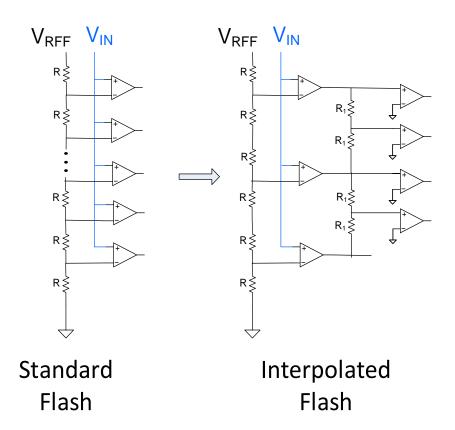

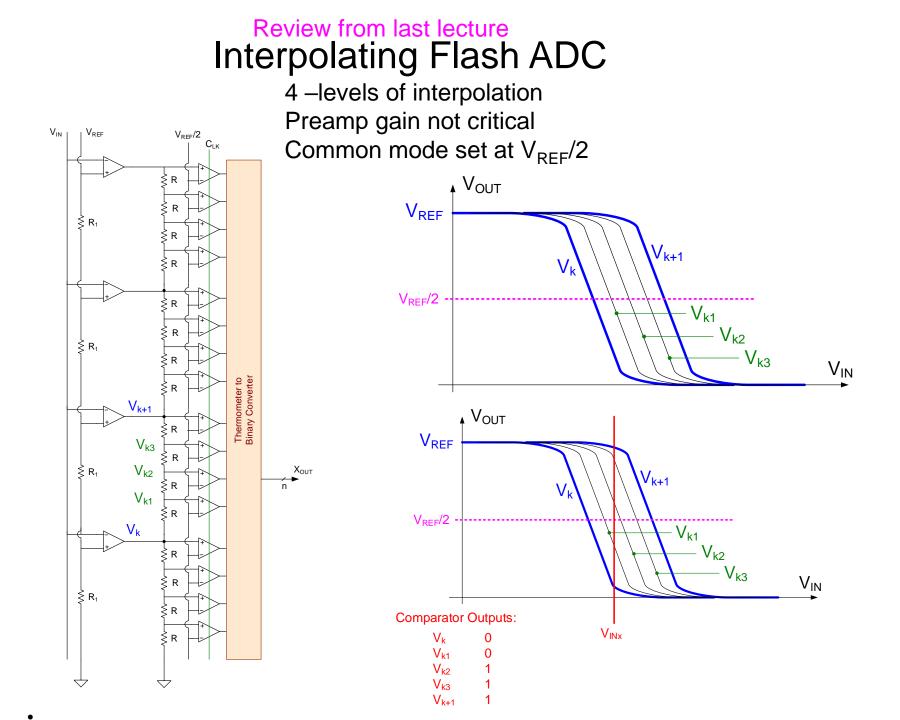

#### Review from last lecture Interpolating Flash ADC

- Reduction in pre-amp area and power

- Latches all referenced to ground

- Loading on V<sub>IN</sub> reduced

- Kickback to V<sub>REF</sub> reduced

- V<sub>IN</sub> coupling to V<sub>REF</sub> reduced

- Multiple levels can be included in interpolator array

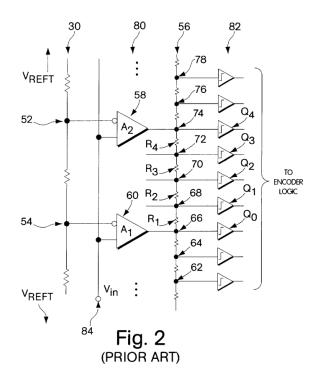

Standard R-String Interpolators

Flying Interpolator

Interpolator can be based upon alternative DAC structures

- Current Steering

- Charge Redistribtion

**Multi-Level Interpolators**

Flash ADC Summary

### Flash ADC

- Very fast Simple structure Usually Clocked Bubble Removal Important Seldom over 6 or 7 bits of resolution

- Flash ADC has some really desirable properties (simple and fast)

- Wouldn't it be nice if we could derive most of the benefits of the FLASH ADC without the major limitations

To be practical at higher resolution, must address the major limitation of the FLASH ADC

Major Limitation of FLASH ADC at higher resolutions?

- Number of comparators increases geometrically --- 2<sup>n</sup>

- String DAC area increases geometrically

- Too many comparators making non-critical decisions increases power

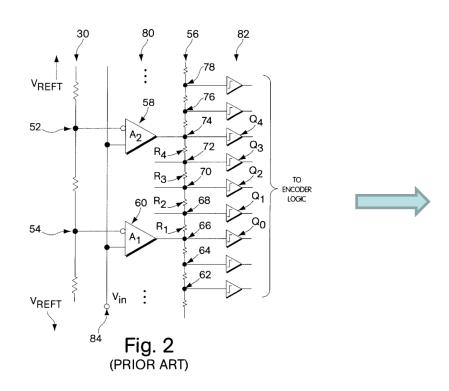

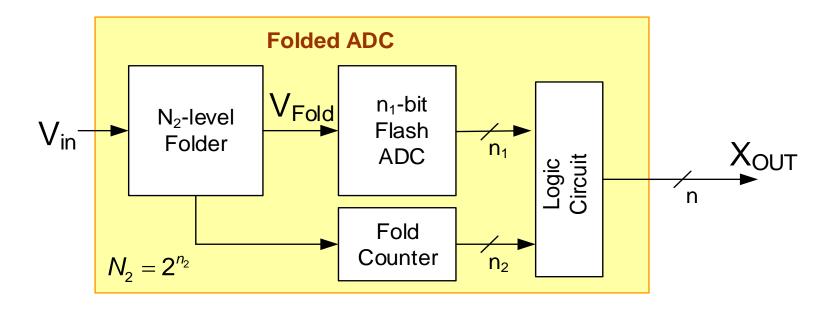

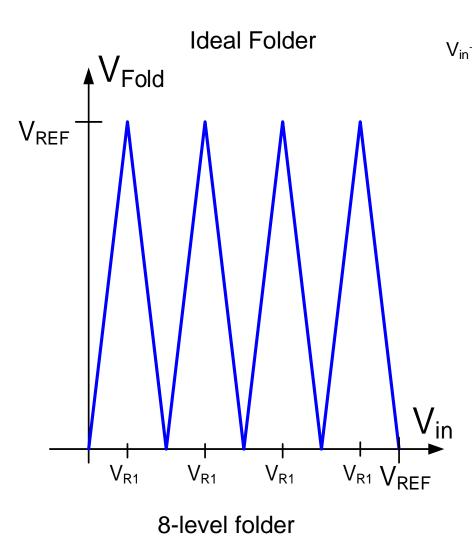

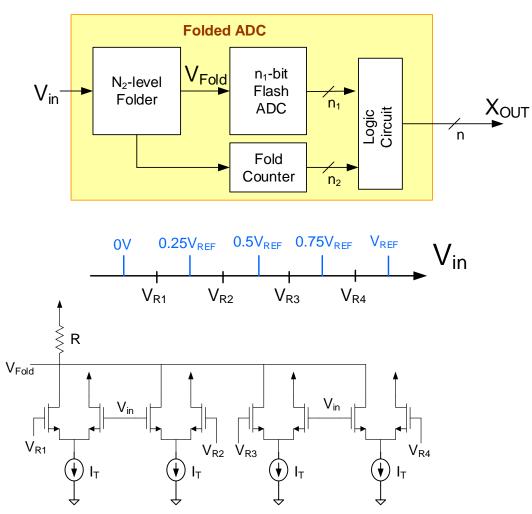

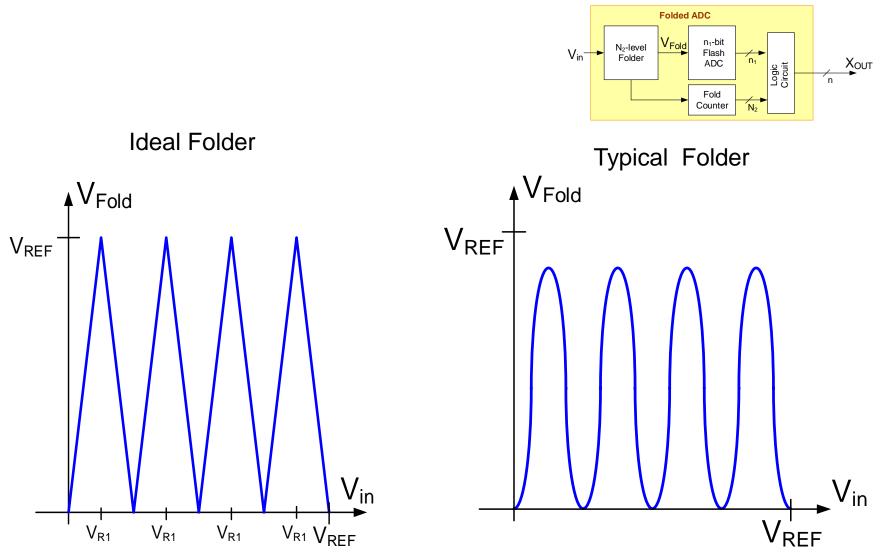

Premise: Folder provides large gain and is very fast

Similar in concept to interpolating flash ADC but

- Number of comparators has been reduced

- Thermometer to Binary decoder is eliminated

- Provides gain in each fold region

- Effective input range increased from  $V_{\text{REF}}$  to  $N_2 V_{\text{REF}}$

- Reduces performance requirements of flash ADC by  $\rm N_2$

- Reduces number of comparators by factor of N<sub>2</sub>

- Performance strongly dependent upon performance of folder

- With fast folders, speed comparable to that of a flash ADC

- Architecture of choice by Phillips (now NXP) for high-speed operation for many years (Rudy van de Plassche)

- Competes with pipeline for performance

- Requires N<sub>2</sub>/2 differential amplifiers

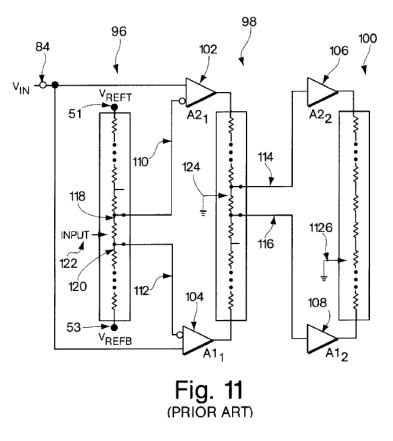

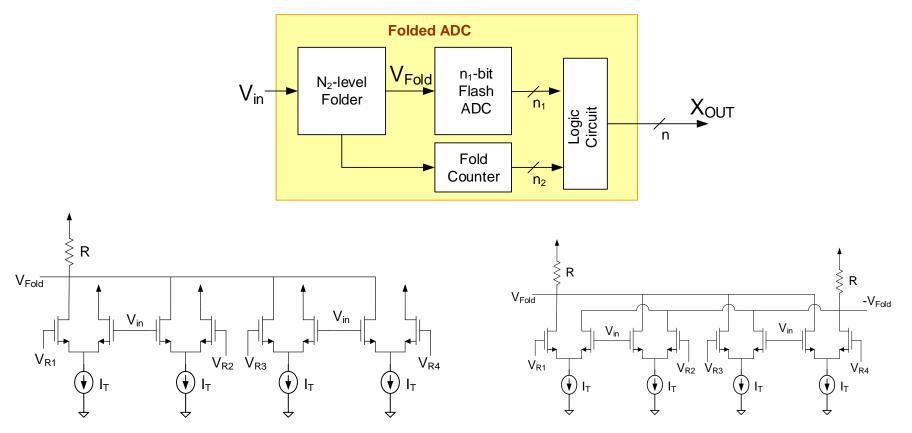

- Basic Folder Circuit (8 level)

- Simple Differential Pair can be very fast

- Usually implemented in differential form

- Differential output almost free

Nonlinearity in folder not a major problem since resolution nonlinearity affects primarily the LSBs and resolution of folded ADCs not large

## Multi-Step Flash Approaches

Goal with Multi-Step Flash Approach:

- Reduce number of comparators and sub DAC levels

- Reduce or eliminate un-necessary comparator decisions

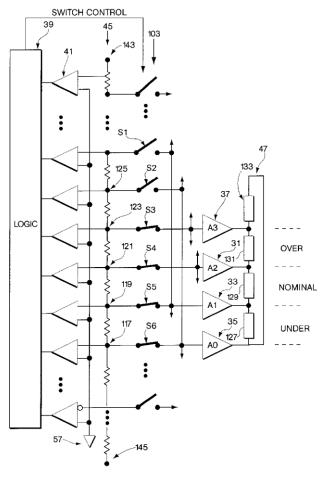

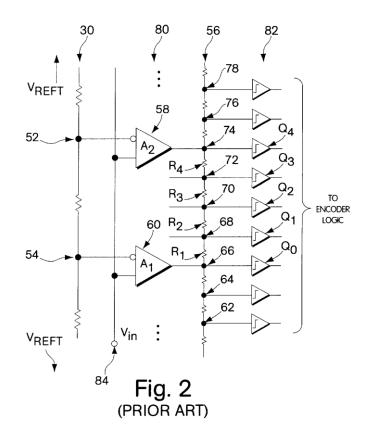

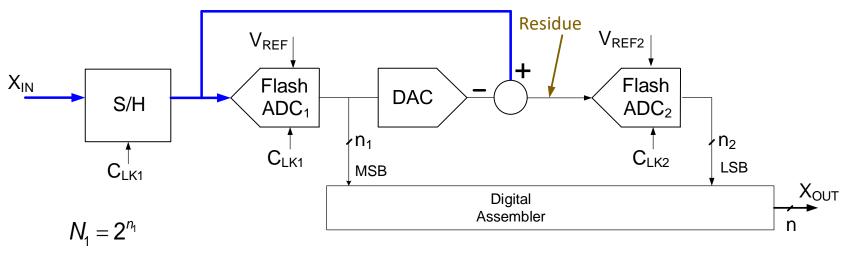

## Two-Step Flash ADC

$N_2 = 2^{n_2}$

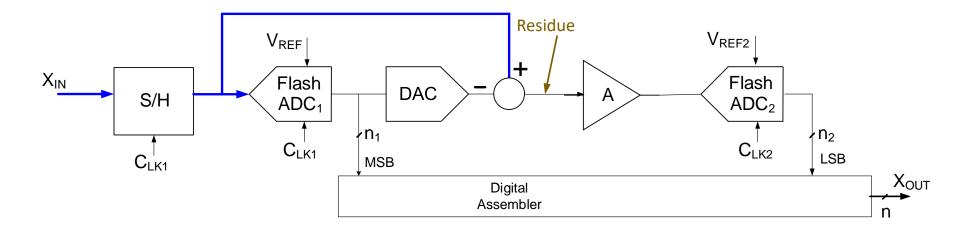

- Can operate asynchronously after S/H

- If clocked, C<sub>LK2</sub> must be delayed from C<sub>LK1</sub>

- Full-range of Residue signal is V<sub>REF</sub>/N<sub>1</sub>

- Reduces number of comparators from  $2^{n_1+n_2}$  to  $2^{n_1}+2^{n_2}$

- $V_{REF2}$  can be reduced by a factor of  $N_1$  from  $V_{REF}$

- No improvement in offset requirements on comparators of second-stage flash

- Common-mode signal swing on comparators in second-stage flash reduced by factor of  $\rm N_1$

- DAC accuracy and difference amplifier performance important

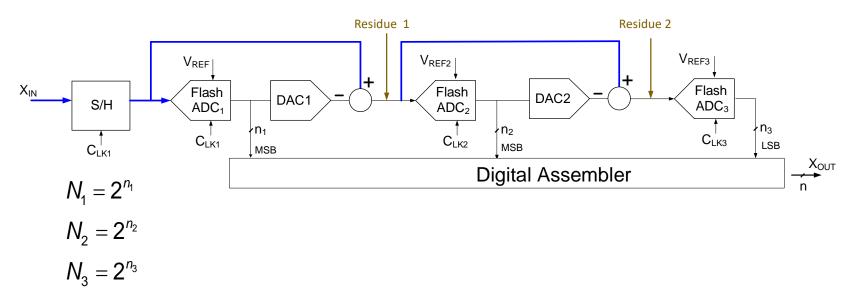

## Three-Step Flash ADC

- Can operate asynchronously after S/H

- Full-range of Residue 2 signal is  $V_{REF}/(N_1N_2)$

- Reduces number of comparators by factor from  $2^{n_1+n_2+n_3}$  to  $2^{n_1}+2^{n_2}+2^{n_3}$

- V<sub>REF3</sub> can be reduced by a factor of N<sub>2</sub> from V<sub>REF2</sub>

- No improvement in offset requirements on comparators of second-stage flash

- Common-mode signal swing on comparators in second-stage flash reduced by factor of  $\ensuremath{\mathsf{N}}_1$

- DAC accuracy and difference amplifier performance important

# Two-Step Flash ADC with Interstage Gain

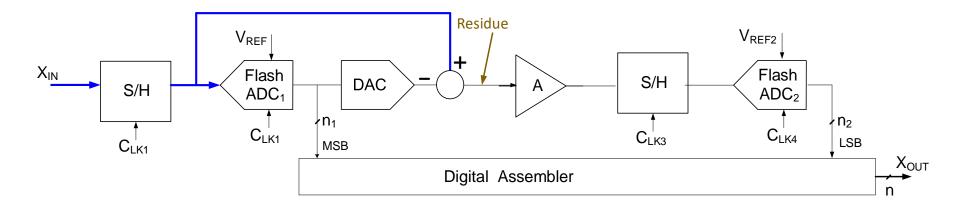

# Two-Step Flash ADC with Interstage Gain and S/H

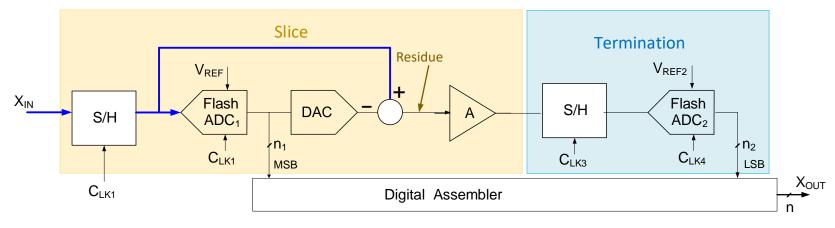

Slice which could be repeated

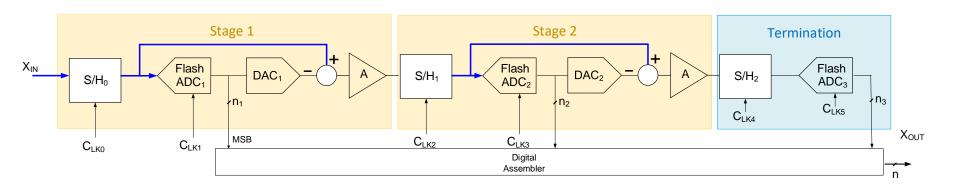

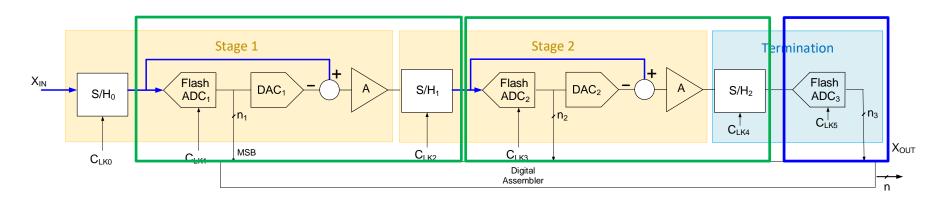

### Three-Step Flash ADC with Interstage Gain and S/H

- S/H frees first stage to take another sample during second stage conversion

- This has a pipelining capability

- The pipelined approach dramatically improves speed (close to Flash)

- Significantly reduces the number of comparators

- Introduces latency but not of concern in most applications

## Three-Step Flash ADC with Interstage Gain

### Can be extended to more than 3 stages

- Can go up to 16 bits or maybe a little higher

- Could be as few as one comparator in each Flash ADC

- Further reduction in number of comparators

(e.g. if one comparator per stage, need only n comparators)

- More latency with more stages but still seldom of concern

- If gains are large enough, comparator offsets in later states can be large

- Will show that with minor modifications, comparator offsets can even be large in first stage

Can partition stages differently

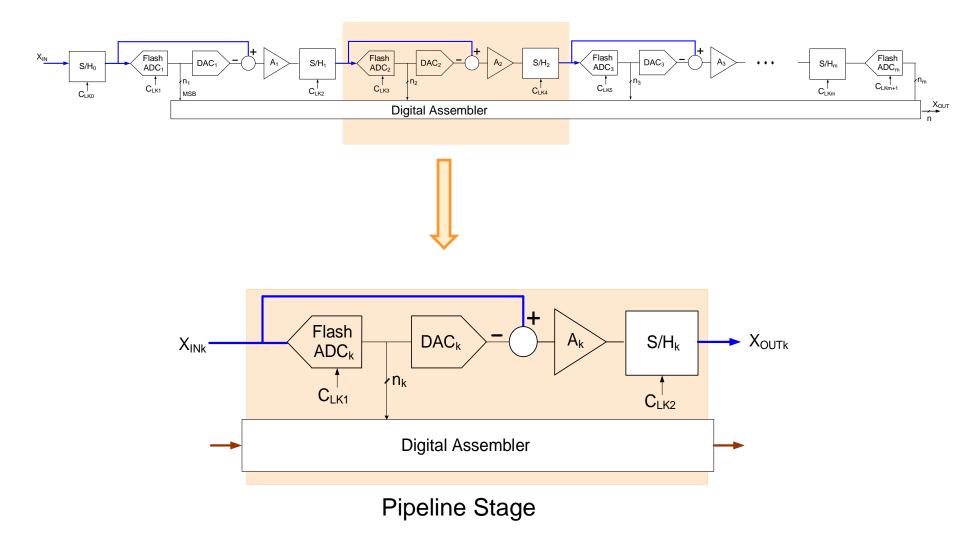

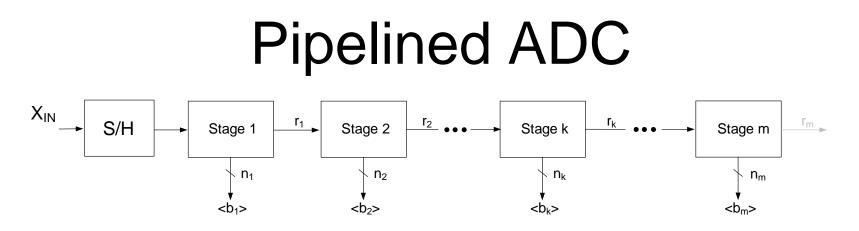

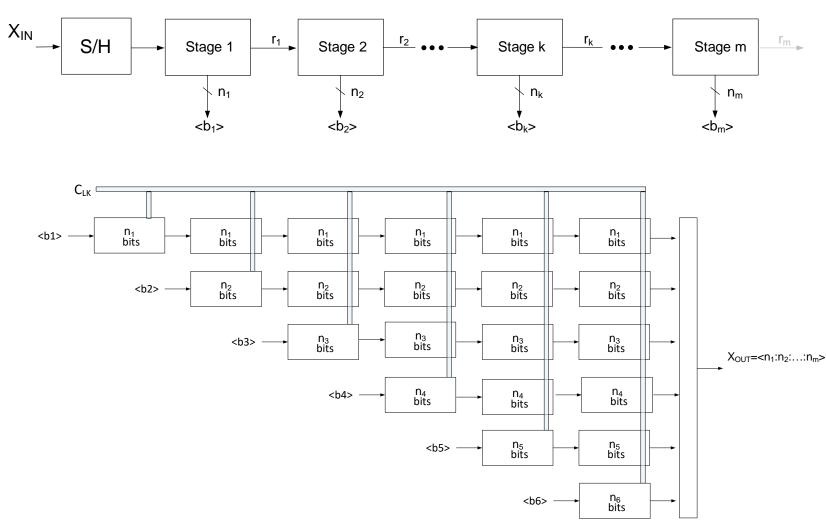

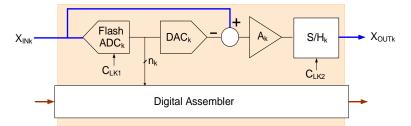

### **Pipelined ADC**

Digital Assembler can simply concatenate individual outputs for some stage architectures  $X_{OUT} = < n_1: n_2: ...: n_m >$

In this case the Digital Assembler can be a set of m-parallel shift-register blocks with output on the last stage

Latency is equal to the number of stages times the conversion time/stage

# **Pipelined ADC**

**Digital Assembler**

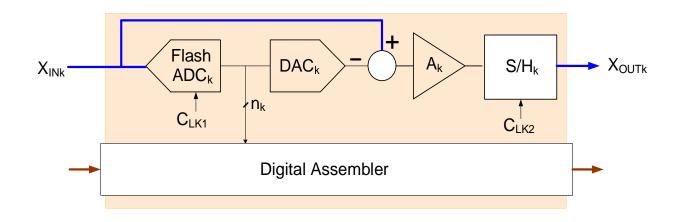

## **Pipeline Stage**

- Appears to be lots of complexity

- S/H is sampling a near-static signal on all stages (except stage 0)

- Ideally the stage gain is chosen so for maximum signal level at the output is V<sub>REF</sub> for each stage

- Dominant source of power dissipation is typically the amplifier

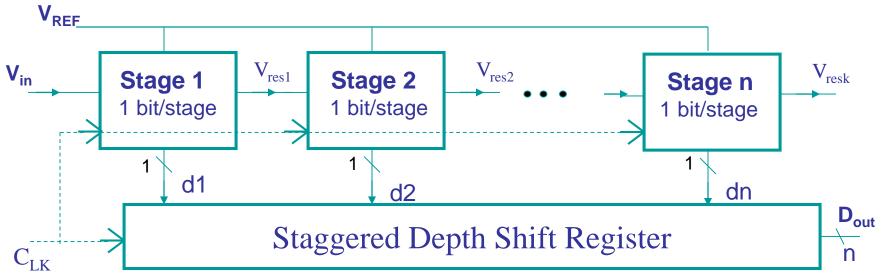

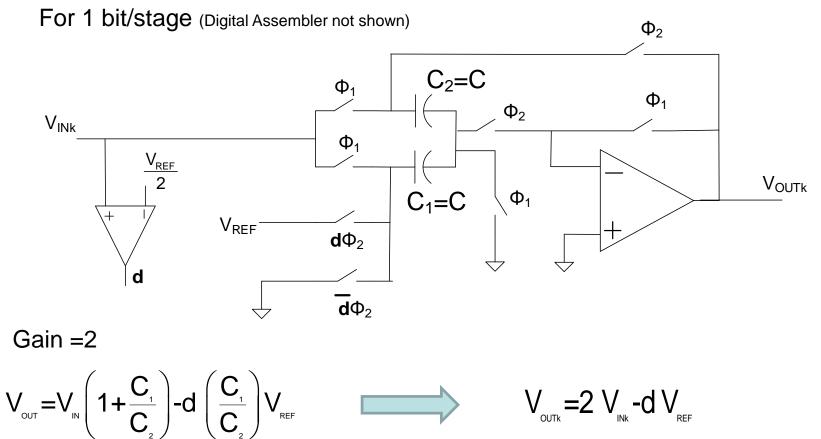

# Example of 1 bit/stage pipeline

- A=2

- ADC is simply comparator in each stage

- Stages could be identical though often relaxed requirements on latter stages to reduce power

- D<sub>OUT</sub> = <d1 d2 ... dn>

- •Functional form of output particularly attractive and simple

- $V_{OUT} = V_{REF} \sum_{i=1}^{n} \frac{a_i}{2^i}$ •Similar relationship for any integral number of bits/stage

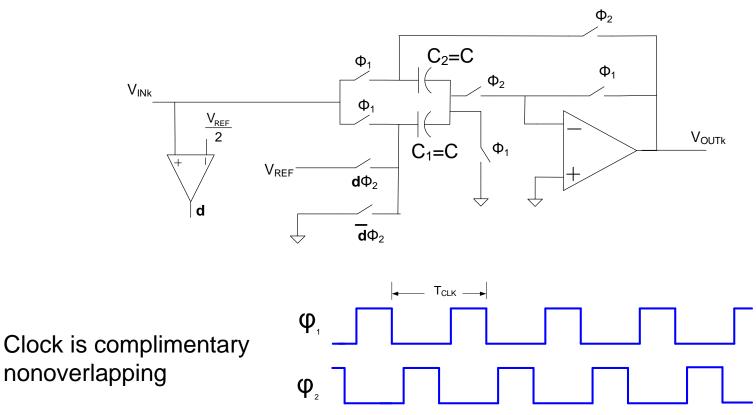

## **Typical SC Pipeline Stage**

Very simple and compact stages are used

For 1 bit/stage (Digital Assembler not shown)

## **Typical SC Pipeline Stage**

Very simple and compact stages are used

# End of Lecture 22